DDR3 Controller with VHDL

Table of Contents

Brief Description

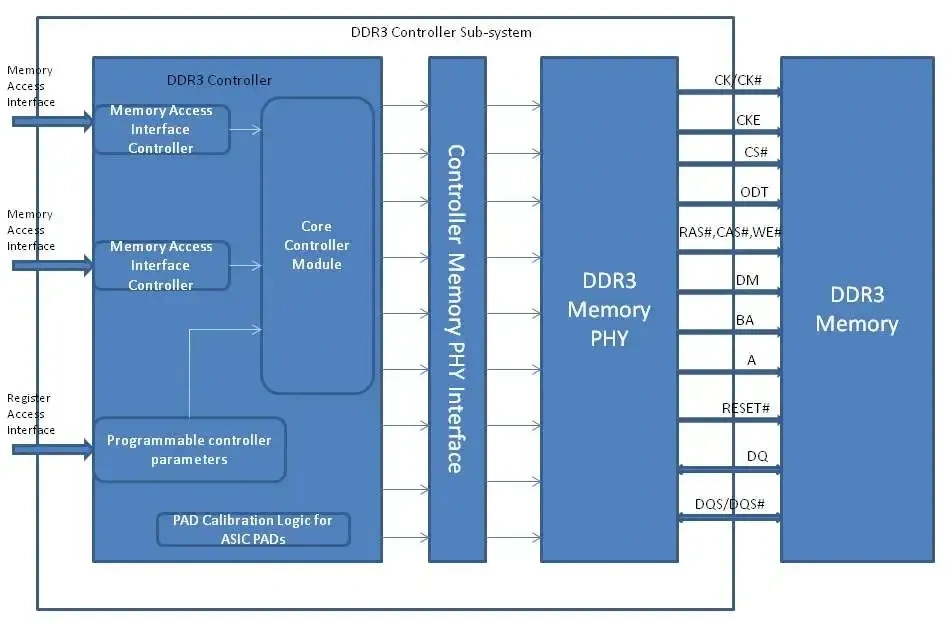

This is a 4:1 memory controller with configurable timing parameters and mode registers so it can be configured to any DDR3 memory device. The user-interface is the basic Wishbone. Optional features include:

AXI4 User Interface

SECDEC for error correction

Self-Refresh

Dual-rank Support

This memory controller is optimized to maintain a high data throughput and continuous sequential burst operations. The controller handles the reset sequence, refresh sequence, mode register configuration, bank status tracking, timing delay tracking, command issuing, and the PHY's calibration. The PHY's calibration handles the bitslip training, read-DQ/DQS alignment via MPR (read calibration), write-DQ/DQS alignment via write leveling (write calibration), and also an optional comprehensive read/write test.

The optional built-in self read/write tests made it easier to test the memory controller without needing an external CPU. These tests include a burst access, random access, and alternating read-write access tests. Only if no error is found on these tests will the calibration end and user can start accessing the wishbone interface.

Like this project

Posted Jan 26, 2025

Opensource DDR3 Controller. Contribute to AngeloJacobo/UberDDR3 development by creating an account on GitHub.

Likes

0

Views

30